# FreeRange Computer Design: The RISC-V Otter MCU

Version: v10.10

©Copyright: 2020 James Mealy

# **Table of Contents**

| ТА | BLE ( | OF CO    | ITENTS                                                  | 2 -  |

|----|-------|----------|---------------------------------------------------------|------|

| PR | ETEN  | NTIONS   |                                                         | 11 - |

|    | Lega  | L CRAP . |                                                         | 11 - |

|    |       |          | GEMENTS                                                 |      |

|    |       |          | OMMENTARY                                               |      |

|    | OVER  | RVIEW O  | F CHAPTER OVERVIEWS                                     | 15 - |

| PA | RT O  | NE: IN   | TRODUCTION AND REVIEW                                   | 19 - |

| 1  | FI    | REERA    | NGE COMPUTER DESIGN OVERVIEW                            | 20 - |

|    | 1.1   |          | DUCTION                                                 |      |

|    | 1.2   |          | TER STRUCTURE                                           |      |

|    | 1.3   |          | ange Computer Design Beginnings                         |      |

|    | 1.4   |          | WITH "MODERN COMPUTER DESIGN"                           |      |

|    | 1.5   | The R    | AT MICROCONTROLLER/MICROCOMPUTER                        | 22 - |

|    | 1.6   | The R    | ISC-V OTTER MCU                                         | 23 - |

|    | 1.7   | ISSUES   | WITH THE CPE 233 COURSE                                 |      |

|    | 1.    | .7.1     | The CPE 233 Approach                                    |      |

|    | 1.8   | Снар     | er Summary                                              | 25 - |

|    | 1.9   | Снар     | FER EXERCISES                                           | 26 - |

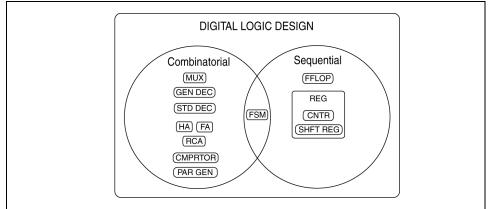

| 2  | D     | IGITAL   | DESIGN REVIEW                                           | 27 - |

|    | 2.1   | Intro    | DUCTION                                                 | 27 - |

|    | 2.2   | The D    | esign Process                                           | 27 - |

|    | 2.3   | THE N    | ew Digital Paradigm: Digital Design Foundation Modeling | 28 - |

|    | 2.    | .3.1     | DDFM Overview                                           | 28 - |

|    | 2.    | .3.2     | The Three Approaches to Digital Design                  | 30 - |

|    | 2.    | .3.3     | Notes on Modular Design Techniques                      | 31 - |

|    | 2.4   | IMPOR    | RTANT DIGITAL VOCABULARY                                | 32 - |

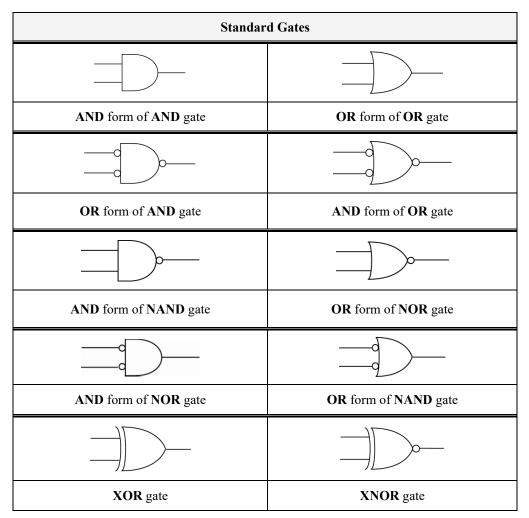

|    | 2.5   | BASIC    | GATES                                                   | 34 - |

|    | 2.6   | Соме     | INATORIAL CIRCUITS                                      | 36 - |

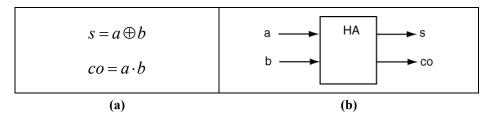

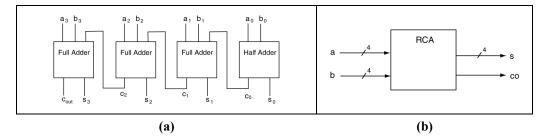

|    | 2.    | .6.1     | Half Adder                                              | 36 - |

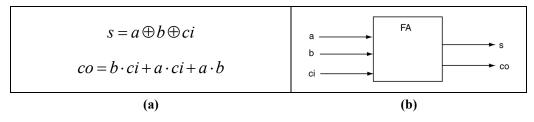

|    | 2.    | .6.2     | Full Adder                                              | 37 - |

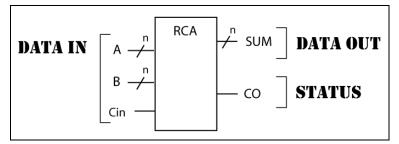

|    | 2.    | .6.3     | Ripple Carry Adder                                      | 37 - |

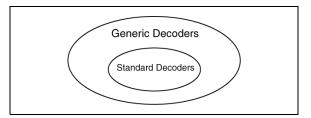

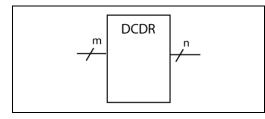

|    | 2.    | .6.4     | Decoders                                                | 38 - |

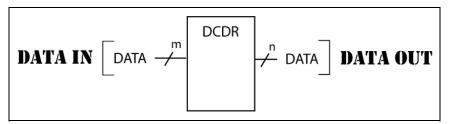

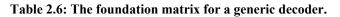

|    |       | 2.6.4.   | 1 Generic Decoder                                       | 39 - |

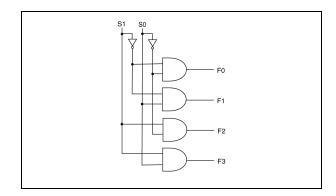

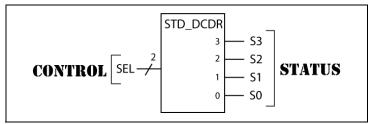

|    |       | 2.6.4.   | 2 Standard Decoder                                      | 40 - |

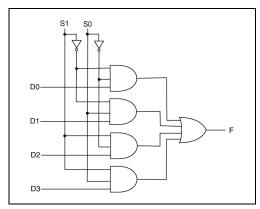

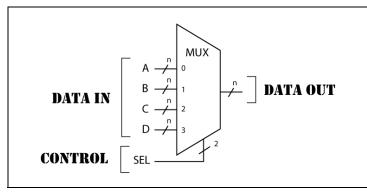

|    | 2.    | .6.5     | Multiplexor                                             | 41 - |

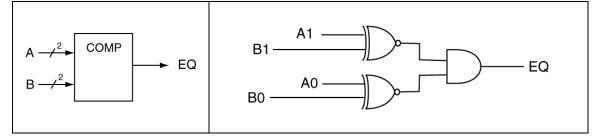

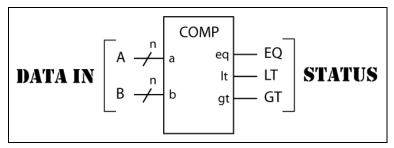

|    | 2.    | .6.6     | Comparator                                              | 43 - |

|    | 2.7   | Sequi    | INTIAL CIRCUITS                                         |      |

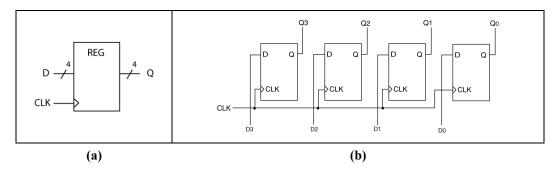

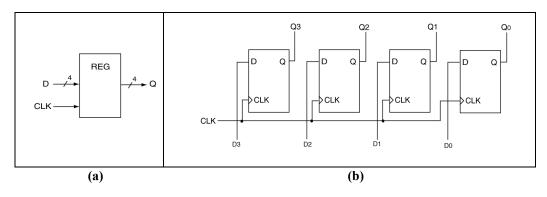

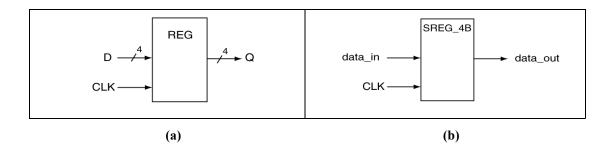

|    | 2.    | .7.1     | Simple Registers                                        |      |

|    |       | 2.7.1.   |                                                         |      |

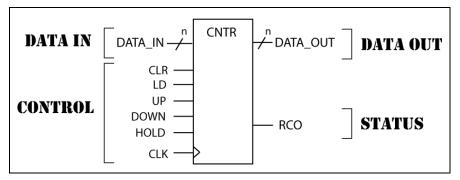

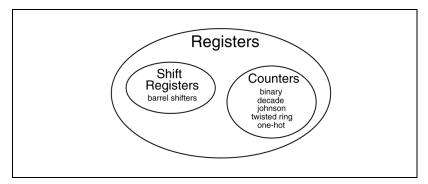

|    |       | .7.2     | Counters: Registers with Features                       |      |

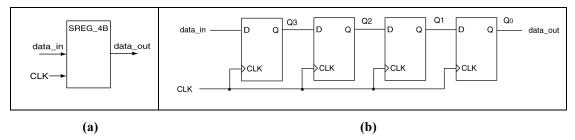

|    |       | .7.3     | Shift Registers                                         |      |

|    |       | .7.4     | Registers: The Final Comments                           |      |

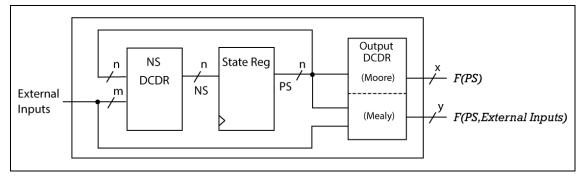

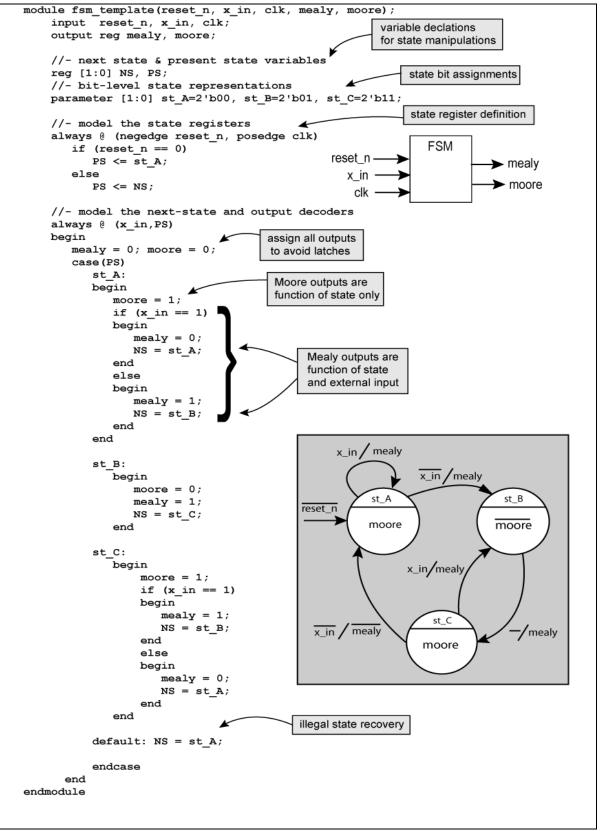

|    | 2.8   |          | STATE MACHINES (FSMs)                                   |      |

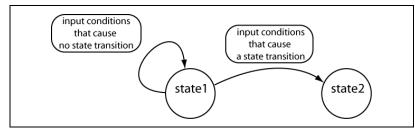

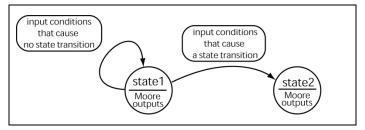

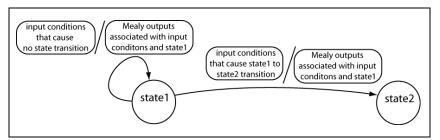

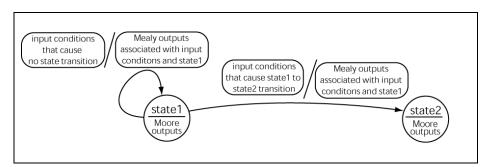

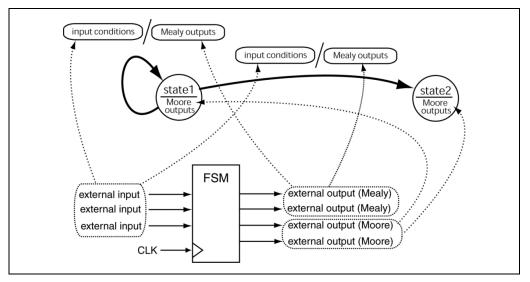

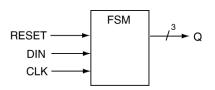

|    |       | .8.1     | High-Level Modeling of Finite State Machines            |      |

|    | 2.    | .8.2     | The FSM: Symbology Overview                             |      |

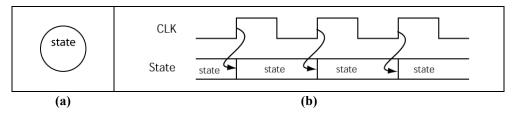

|    |       | 2.8.2.   | 1 The State Bubble                                      | 54 - |

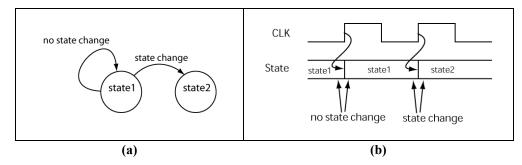

|    |            | 2.8.2.2 |                                                                |        |

|----|------------|---------|----------------------------------------------------------------|--------|

|    |            | 2.8.2.3 | ····· · · · · · · · · · · · · · · · ·                          |        |

|    |            | 2.8.2.4 |                                                                |        |

|    |            | 2.8.2.5 |                                                                |        |

|    |            | 2.8.2.6 |                                                                |        |

|    |            | 2.8.2.7 |                                                                |        |

|    | 2.9        |         | ER SUMMARY                                                     |        |

|    | 2.10       |         | APTER EXERCISES                                                |        |

|    | 2.11       | Сн      | APTER DESIGN PROBLEMS                                          | 62 -   |

| 3  | Α          | DVANC   | ED REGISTERS                                                   | 63 -   |

|    | 3.1        | INTRO   | DUCTION                                                        | 63 -   |

|    | 3.2        | Regist  | ERS: THE MOST COMMON DIGITAL CIRCUIT EVER?                     | 63 -   |

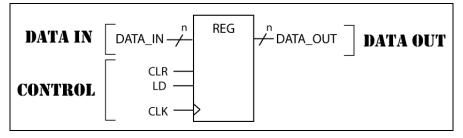

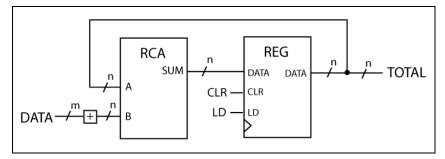

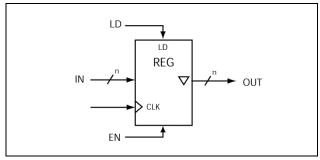

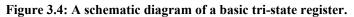

|    | 3.3        |         | ATE REGISTERS                                                  |        |

|    | 3.4        |         | ectional Registers                                             |        |

|    | 3.5        |         | Registers                                                      |        |

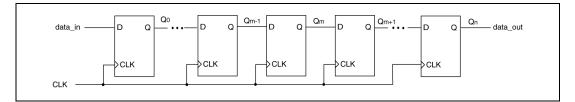

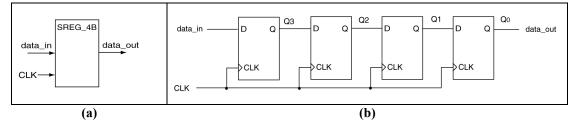

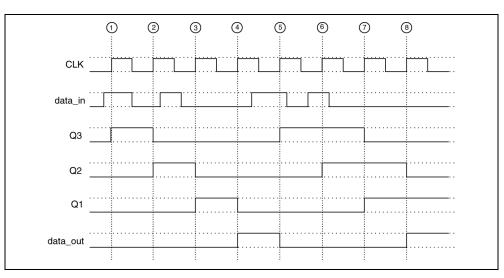

|    | .3.        |         | Basic Shift Registers                                          |        |

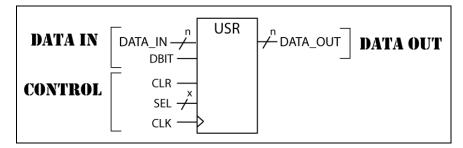

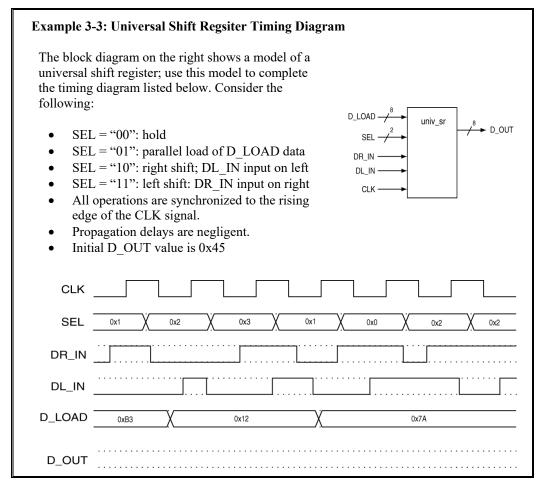

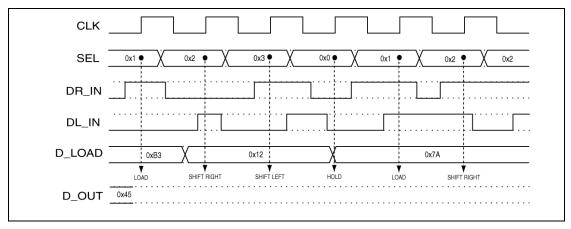

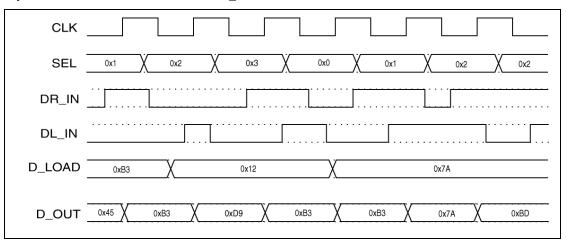

|    | -          | 5.2     | Universal Shift Registers                                      |        |

|    | -          | -       | Barrel Shifters                                                |        |

|    | -          | 5.4     | Other Shift Register-Type Features                             |        |

|    | 3.6        | -       | ER SUMMARY                                                     |        |

|    | 3.7        |         | ER SUMIMARY                                                    |        |

|    | -          | -       |                                                                |        |

| P/ | ART T      | WO: AI  | OVANCED DIGITAL DESIGN                                         | - 84 - |

| 4  | C          |         | R: REGISTER TRANSFER NOTATION                                  | _ 95 _ |

| 4  | CI         |         |                                                                |        |

|    | 4.1        |         | DUCTION                                                        |        |

|    | 4.2        | Regist  | er Transfer Notation Specifics                                 | 85 -   |

|    | 4.3        | MICRO   | OPERATIONS AND DATA TRANSFERS                                  | 89 -   |

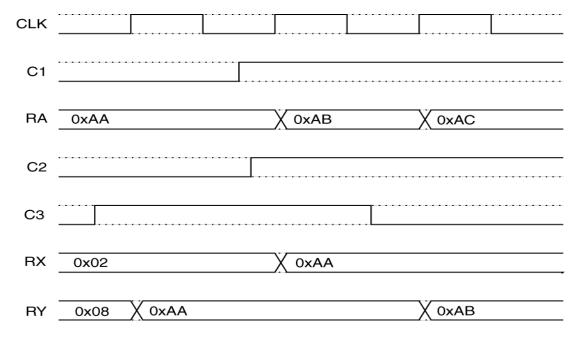

|    | 4.         | 3.1     | Transfer Microoperations                                       | 89 -   |

|    | 4.         | 3.2     | Arithmetic Microoperations                                     | 90 -   |

|    | 4.         | 3.3     | Logic Microoperations                                          | 90 -   |

|    | 4.         | 3.4     | Shift Microoperations                                          | 91 -   |

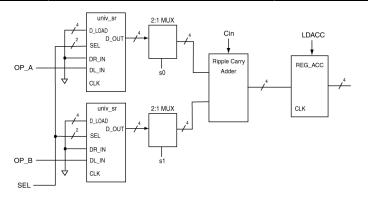

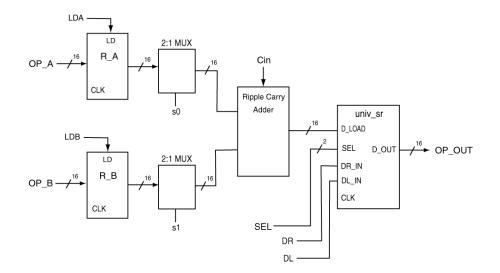

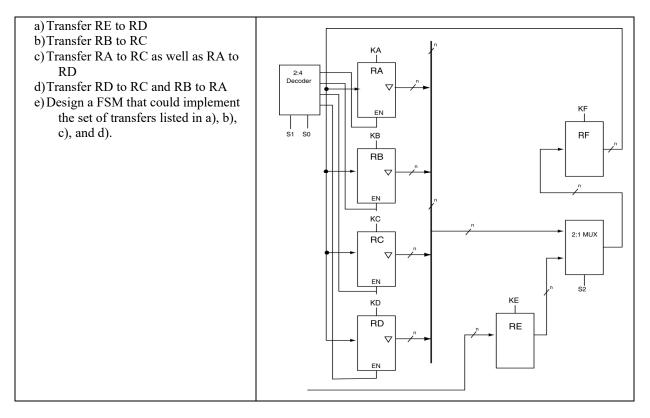

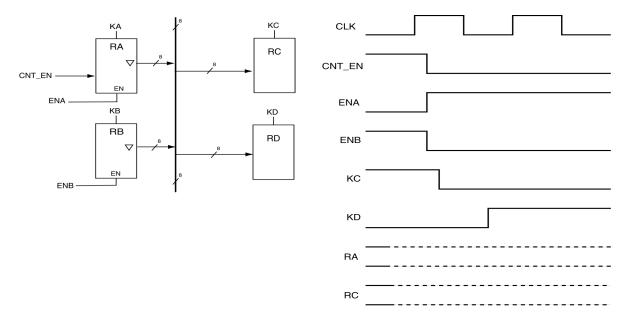

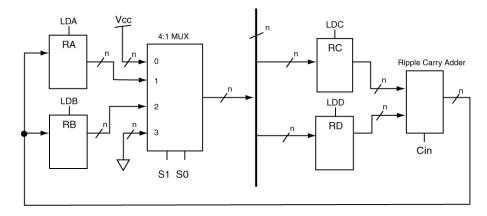

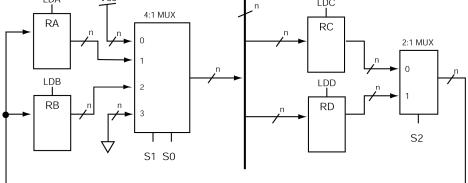

|    | 4.4        |         | Fransfer Circuits                                              |        |

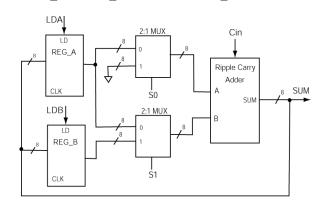

|    |            |         | MUX-Based Data Transfers                                       |        |

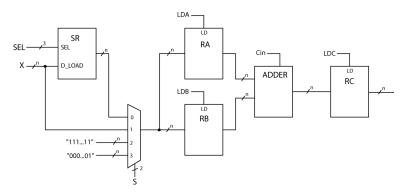

|    |            |         | Bus-Based Data Transfers                                       |        |

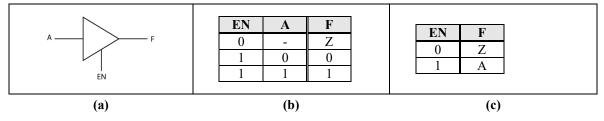

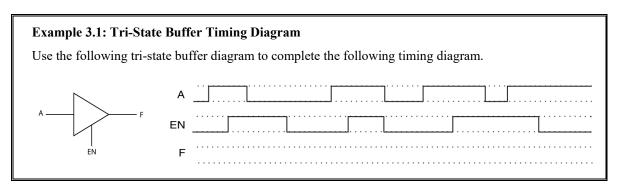

|    |            | 4.3     | Tri-State Bus-Based Transfers                                  |        |

|    | 45         | Снарт   | ER SUMMARY                                                     |        |

|    | 4.6        |         | HAPTER EXERCISES                                               |        |

| _  |            | -       |                                                                |        |

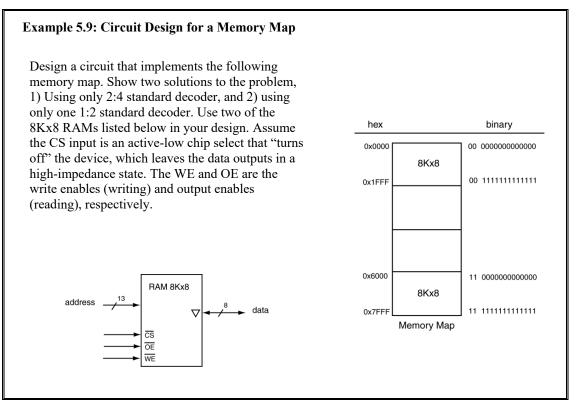

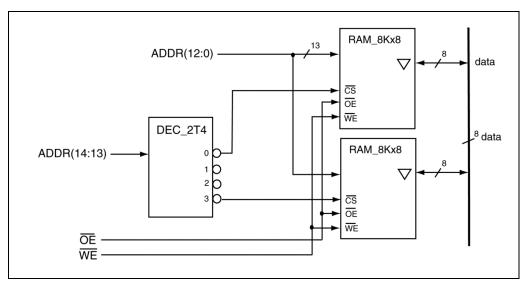

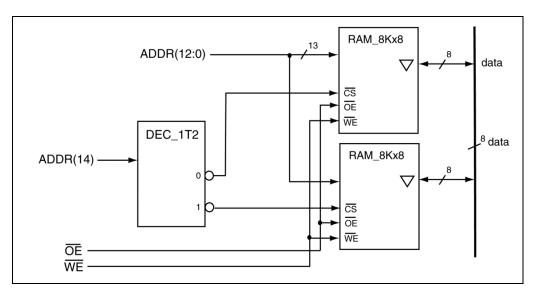

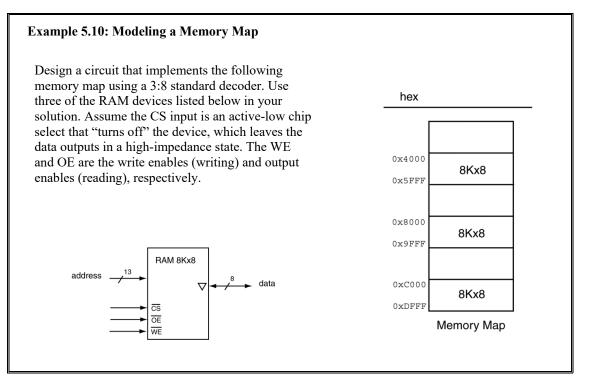

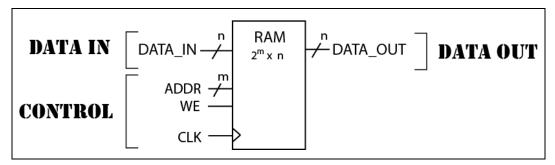

| 5  | S          | IRUCTI  | JRED MEMORY: RAM AND ROM                                       | 112 -  |

|    | 5.1        | Intro   | DUCTION                                                        | 112 -  |

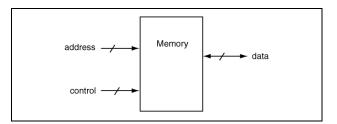

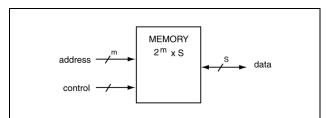

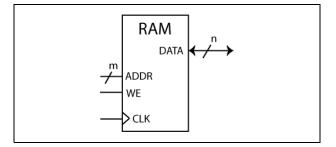

|    | 5.2        | Мемс    | RY INTRODUCTION AND OVERVIEW                                   | 112 -  |

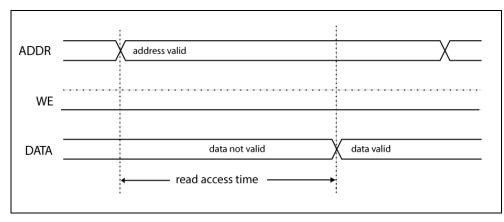

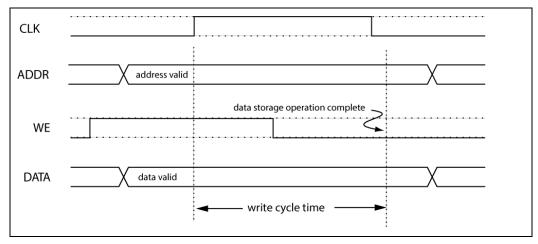

|    | 5.         | 2.1     | Basic Memory Operations: READ and WRITE                        | 113 -  |

|    | 5.         |         | Basic Memory Types: ROM and RAM                                |        |

|    | 5.3        |         | ARE ARRAYS VS. HARDWARE STRUCTURED MEMORIES                    |        |

|    | 5.4        | Мемс    | RY OPERATION DETAILS: READING AND WRITING                      | 114 -  |

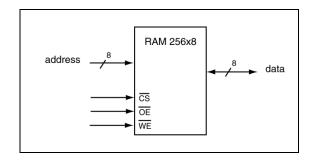

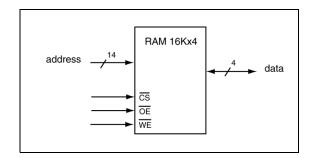

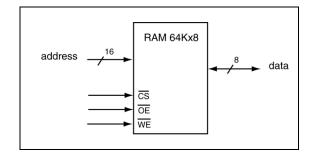

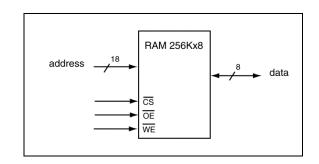

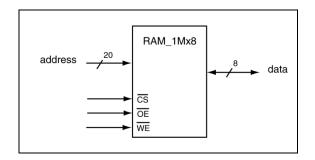

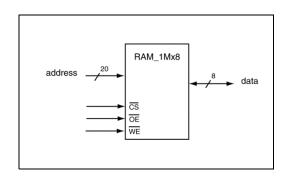

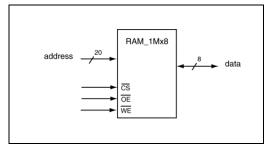

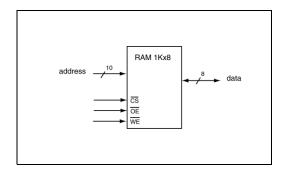

|    | 5.5        |         | RY SPECIFICATION AND CAPACITY                                  |        |

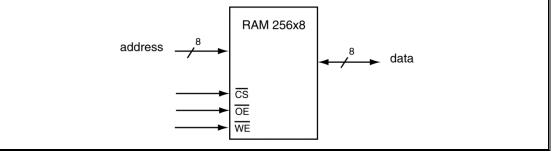

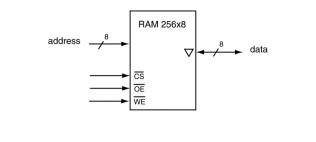

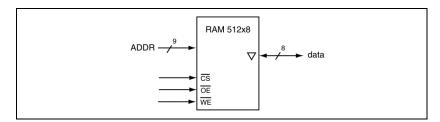

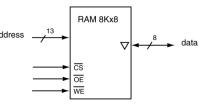

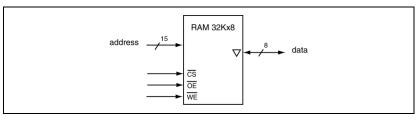

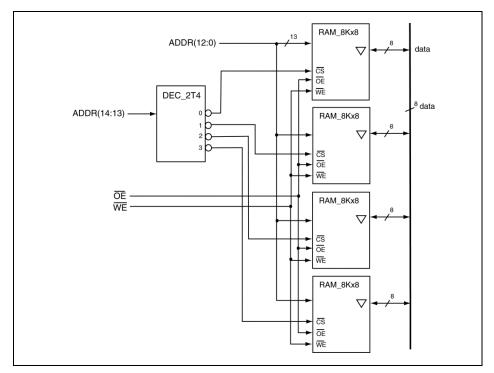

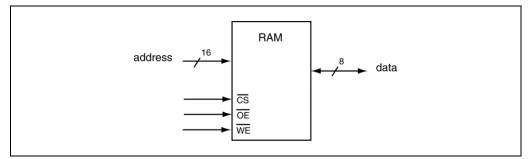

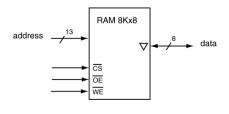

|    | 5.6        |         | INTERFACE DETAILS                                              | -      |

|    | 5.7        |         | RY PERFORMANCE PARAMETERS                                      |        |

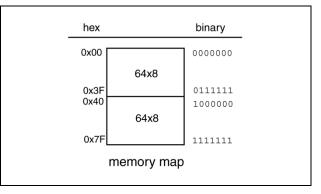

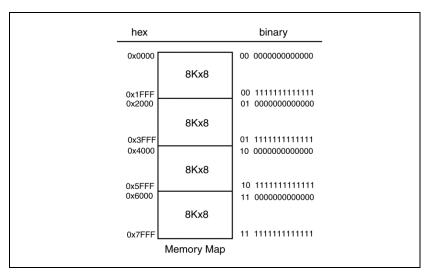

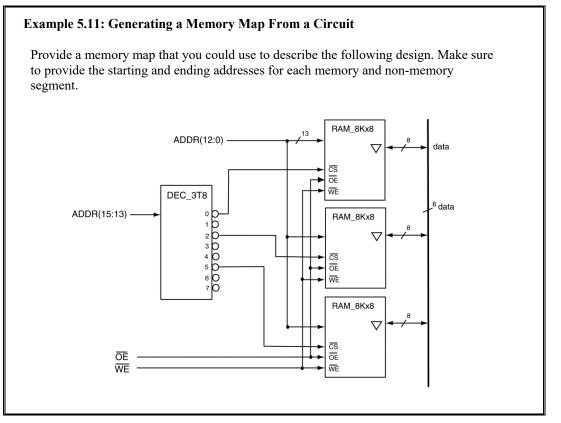

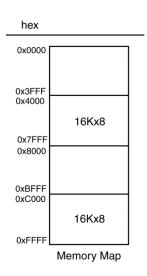

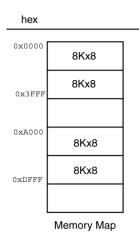

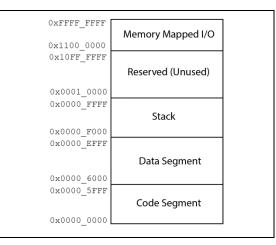

|    | 5.8        |         | RY MAPPING                                                     |        |

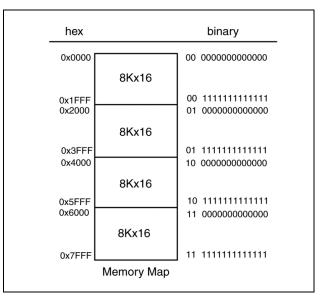

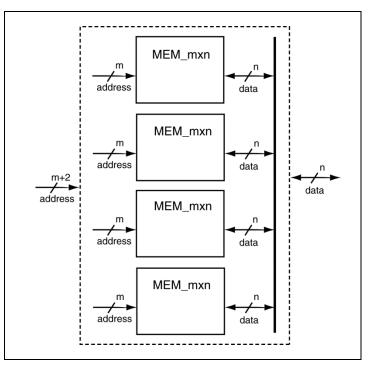

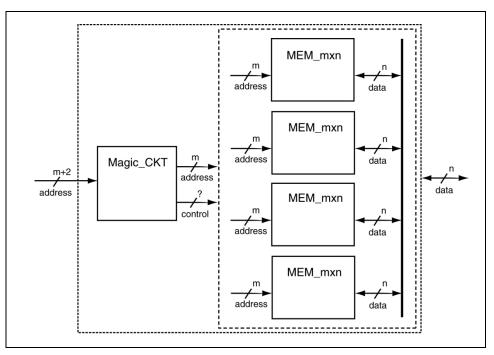

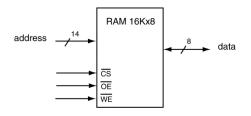

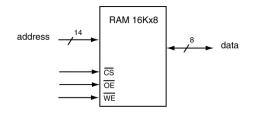

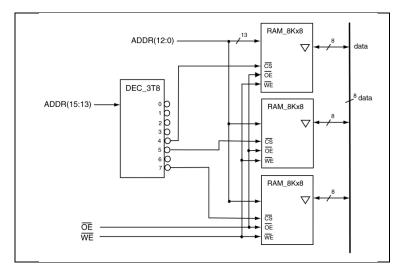

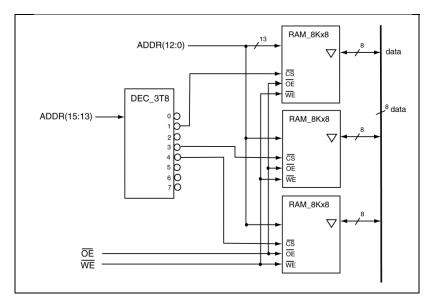

|    | 5.8<br>5.9 |         | IRY ORGANIZATION                                               | -      |

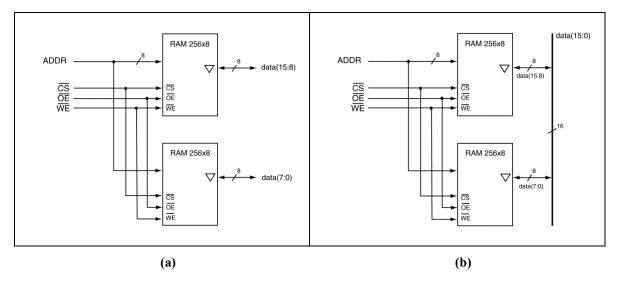

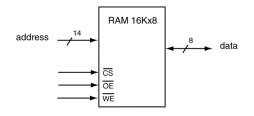

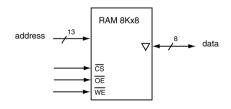

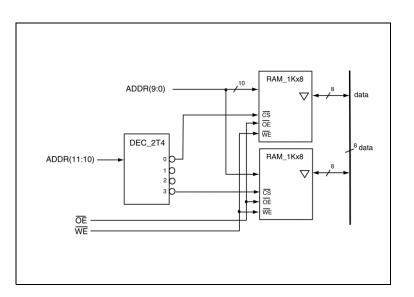

|    |            |         | Extending Memory Word Length                                   | -      |

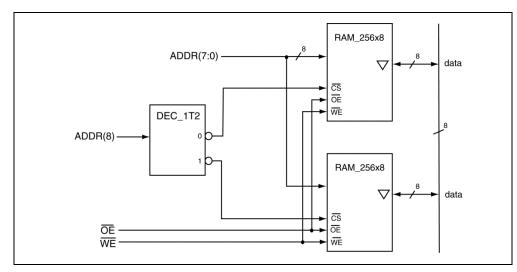

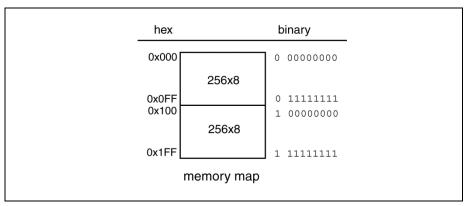

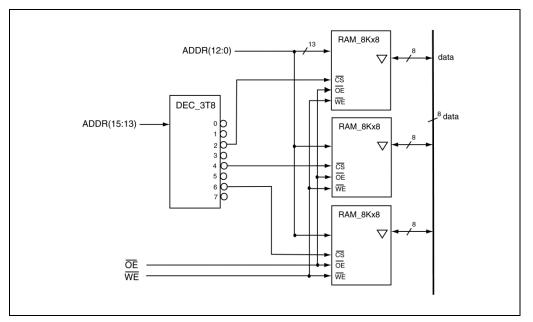

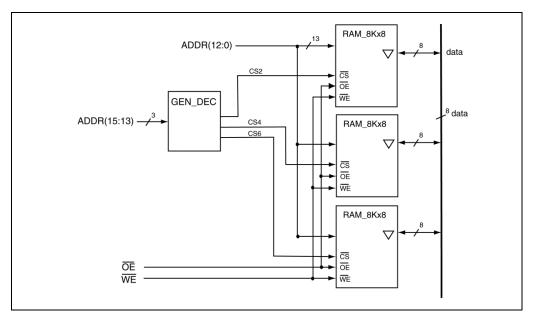

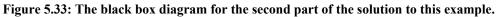

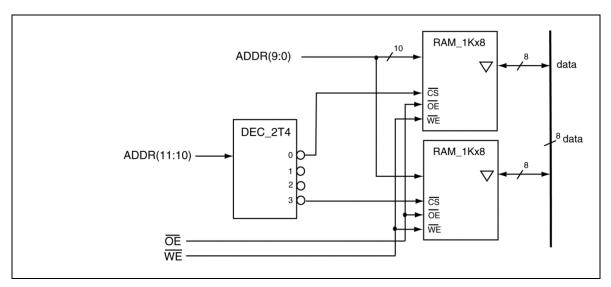

|    | -          |         | Extending Memory Word Length<br>Extending Memory Address Space |        |

|    | э.         | 3.2     | Exterioring wienory Address space                              | 130 -  |

|   | 5.10 DIGITAL DESIGN FOUNDATION NOTATION: RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 143 -                                                                                                                                                                                              |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 5.11 Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 145 -                                                                                                                                                                                              |

|   | 5.12 Chapter Exercises                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                    |

|   | 5.13 Chapter Design Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 154 -                                                                                                                                                                                              |

| P | PART THREE: INTRODUCTION TO COMPUTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 156 -                                                                                                                                                                                              |

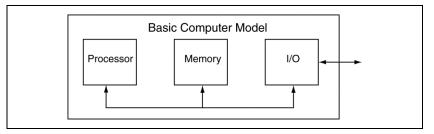

| 6 | 5 THE BASIC COMPUTER IN HIGH-LEVEL TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 157 -                                                                                                                                                                                              |

|   | 6.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 157 -                                                                                                                                                                                              |

|   | 6.2 HIGH-LEVEL VIEW OF LEARNING "DIGITAL STUFF"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                    |

|   | 6.2.1 Solving Problems with Digital Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 157 -                                                                                                                                                                                              |

|   | 6.2.2 Solving Problems with Computers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 158 -                                                                                                                                                                                              |

|   | 6.2.3 Final Problem Solving Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                    |

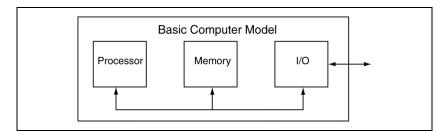

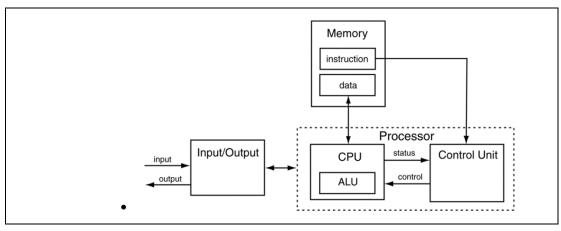

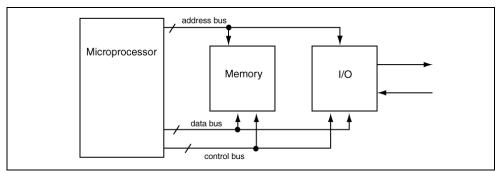

|   | 6.3 What is a Computer?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                    |

|   | 6.4 You and the Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                    |

|   | 6.5 Computer Architecture: For the Hardware People                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                    |

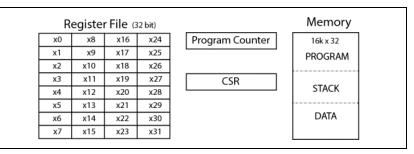

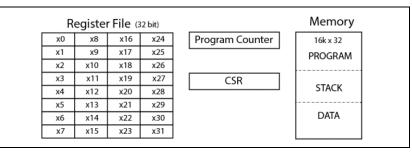

|   | 6.6 COMPUTER ARCHITECTURE: FOR THE PROGRAMMER PEOPLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                    |

|   | 6.6.1 Programmer's Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                    |

|   | 6.6.2 Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                    |

|   | 6.6.3 Computer Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                    |

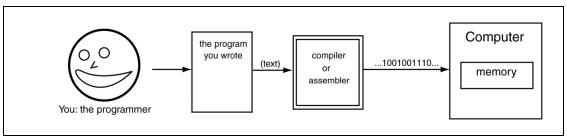

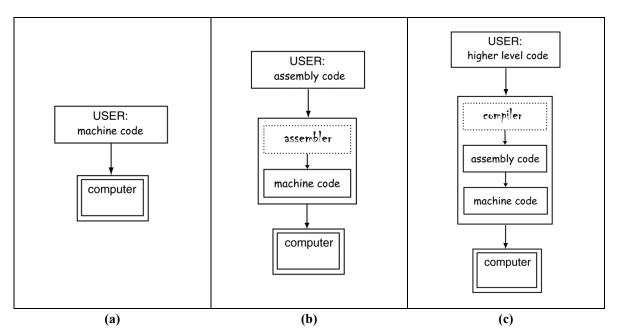

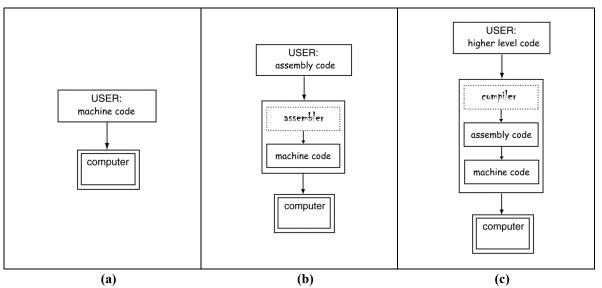

|   | 6.7 Programming Language Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                    |

|   | 6.7.2 Assembly Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                    |

|   | 6.7.3 Higher Level Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                    |

|   | 6.8 The Digital Design Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                    |

|   | 6.9 Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                    |

|   | 6.10 Chapter Exercises                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                    |

| р | PART FOUR: RISC-V ASSEMBLY LANGUAGE PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                    |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | - 168 -                                                                                                                                                                                            |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                    |

| 7 | ASSEMBLY LANGUAGE INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 169 -                                                                                                                                                                                              |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>169 -</b><br>169 -                                                                                                                                                                              |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b> 169 -</b><br>169 -<br>169 -                                                                                                                                                                    |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>169 -</b><br>169 -<br>169 -<br>170 -                                                                                                                                                            |

|   | <ul> <li>ASSEMBLY LANGUAGE INTRODUCTION</li> <li>7.1 INTRODUCTION</li> <li>7.2 BITS TO MNEMONICS AND BACK AGAIN</li> <li>7.3 PROGRAMMING LANGUAGE LEVELS</li> <li>7.3.1 Machine Code</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>169</b> -<br>169 -<br>169 -<br>170 -<br><i>170</i> -                                                                                                                                            |

|   | <ul> <li>ASSEMBLY LANGUAGE INTRODUCTION</li> <li>7.1 INTRODUCTION</li> <li>7.2 BITS TO MNEMONICS AND BACK AGAIN</li> <li>7.3 PROGRAMMING LANGUAGE LEVELS</li> <li>7.3.1 Machine Code</li> <li>7.3.2 Assembly Language</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 169 -<br>169 -<br>169 -<br>170 -<br>170 -<br>171 -                                                                                                                                                 |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 169 -<br>169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -                                                                                                                                        |

|   | <ul> <li>ASSEMBLY LANGUAGE INTRODUCTION</li> <li>7.1 INTRODUCTION</li> <li>7.2 BITS TO MNEMONICS AND BACK AGAIN</li> <li>7.3 PROGRAMMING LANGUAGE LEVELS</li> <li>7.3.1 Machine Code</li> <li>7.3.2 Assembly Language</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>169</b> -<br>169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -                                                                                                                        |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages         7.4       Assembly LANGUAGES: THE GOODNESS OF "LOW-LEVEL"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 169 -<br>169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>173 -                                                                                                                      |

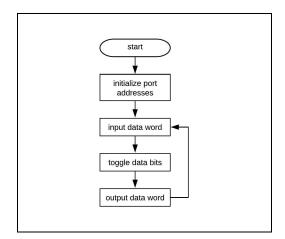

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages         7.4       Assembly LANGUAGES: THE GOODNESS OF "LOW-LEVEL"         7.5       PROBLEM SOLVING WITH PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>173 -<br>175 -                                                                                                                      |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages         7.4       Assembly LANGUAGES: THE GOODNESS OF "LOW-LEVEL"         7.5       PROBLEM SOLVING WITH PROGRAMMING         7.6       STRUCTURED PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>173 -<br>175 -<br>176 -                                                                                                             |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages         7.4       Assembly LANGUAGES: THE GOODNESS OF "LOW-LEVEL"         7.5       PROBLEM SOLVING WITH PROGRAMMING         7.6       STRUCTURED PROGRAMMING         7.7       MOTIVATIONAL DISCUSSION OF FLOWCHARTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>173 -<br>175 -<br>176 -<br>177 -                                                                                                    |

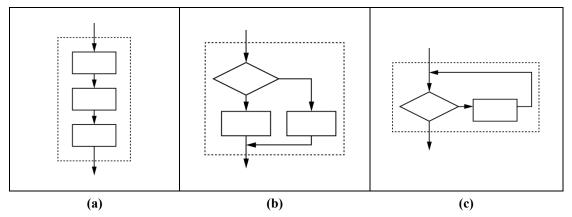

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages         7.4       Assembly LANGUAGES: THE GOODNESS OF "LOW-LEVEL"         7.5       PROBLEM SOLVING WITH PROGRAMMING         7.6       STRUCTURED PROGRAMMING         7.7.1       The Basics of Flowcharting         7.8       STRUCTURED PROGRAMMING REVISITED.         7.8.1       The sequence Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>171 -<br>173 -<br>175 -<br>176 -<br>177 -<br>178 -<br>178 -<br>178 -                                                                |

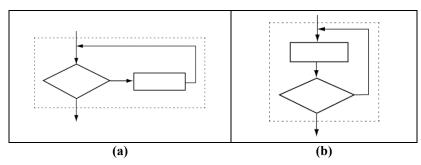

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages         7.4       Assembly LANGUAGES: THE GOODNESS OF "LOW-LEVEL"         7.5       PROBLEM SOLVING WITH PROGRAMMING         7.6       STRUCTURED PROGRAMMING         7.7       MOTIVATIONAL DISCUSSION OF FLOWCHARTING         7.7.1       The Basics of Flowcharting         7.8       STRUCTURED PROGRAMMING REVISITED         7.8.1       The sequence Structure         7.8.2       The if-then-else Structure                                                                                                                                                                                                                                                                                                                                                                                    | 169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>173 -<br>175 -<br>176 -<br>177 -<br>178 -<br>178 -<br>178 -<br>179 -                                                                |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages         7.4       Assembly LANGUAGES: THE GOODNESS OF "LOW-LEVEL"         7.5       PROBLEM SOLVING WITH PROGRAMMING         7.6       STRUCTURED PROGRAMMING         7.7       MOTIVATIONAL DISCUSSION OF FLOWCHARTING         7.7.1       The Basics of Flowcharting         7.8       STRUCTURED PROGRAMMING REVISITED         7.8.1       The sequence Structure         7.8.2       The if-then-else Structure         7.8.3       The iterative Structure                                                                                                                                                                                                                                                                                                                                        | 169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>173 -<br>173 -<br>175 -<br>176 -<br>177 -<br>178 -<br>179 -<br>179 -<br>179 -                                                       |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code.         7.3.2       Assembly Language.         7.3.3       Higher Level Languages         7.4       Assembly Languages:         7.5       PROBLEM SOLVING WITH PROGRAMMING.         7.6       STRUCTURED PROGRAMMING.         7.7       MOTIVATIONAL DISCUSSION OF FLOWCHARTING         7.7.1       The Basics of Flowcharting.         7.8       STRUCTURED PROGRAMMING REVISITED.         7.8.1       The sequence Structure         7.8.2       The if-then-else Structure         7.8.3       The iterative Structure         7.8.3       The iterative Structure         7.8.3       The iterative Structure         7.8.3       The iterative Structure         7.8       The iterative Structure         7.8.3       The iterative Structure         7.8.3       The iterative Structure         7.8.3       The iterative Structure         7.9       THE TRUTH ABOUT SOFTWARE | 169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>171 -<br>173 -<br>175 -<br>175 -<br>177 -<br>178 -<br>179 -<br>179 -<br>180 -                                                       |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages         7.4       Assembly LANGUAGES: THE GOODNESS OF "LOW-LEVEL"         7.5       PROBLEM SOLVING WITH PROGRAMMING         7.6       STRUCTURED PROGRAMMING         7.7       MOTIVATIONAL DISCUSSION OF FLOWCHARTING         7.7.1       The Basics of Flowcharting         7.8       STRUCTURED PROGRAMMING REVISITED         7.8.1       The sequence Structure         7.8.2       The if-then-else Structure         7.8.3       The iterative Structure         7.8.3       The iterative Structure         7.8.3       The iterative Structure         7.9       THE TRUTH ABOUT SOFTWARE         7.9.1       Software Quality                                                                                                                                                                | 169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>171 -<br>173 -<br>175 -<br>175 -<br>177 -<br>178 -<br>179 -<br>179 -<br>180 -<br>180 -<br>180 -                                     |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages         7.4       Assembly Languages:         7.5       PROBLEM SOLVING WITH PROGRAMMING         7.6       STRUCTURED PROGRAMMING         7.7       MOTIVATIONAL DISCUSSION OF FLOWCHARTING         7.7.1       The Basics of Flowcharting.         7.8       STRUCTURED PROGRAMMING REVISITED.         7.8.1       The sequence Structure         7.8.2       The if-then-else Structure.         7.8.3       The iterative Structure.         7.8.3       The iterative Structure.         7.9       THE TRUTH ABOUT SOFTWARE         7.9.1       Software Quality         7.10       WRITING GOOD PROGRAMS                                                                                                                                                                                          | 169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>171 -<br>173 -<br>175 -<br>176 -<br>177 -<br>178 -<br>178 -<br>179 -<br>180 -<br>180 -<br>180 -<br>180 -<br>180 -<br>180 -<br>180 - |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages         7.4       Assembly Languages: The GOODNESS OF "Low-LEVEL"         7.5       PROBLEM SOLVING WITH PROGRAMMING         7.6       STRUCTURED PROGRAMMING         7.7       MOTIVATIONAL DISCUSSION OF FLOWCHARTING         7.7.1       The Basics of Flowcharting.         7.8       STRUCTURED PROGRAMMING REVISITED.         7.8.1       The sequence Structure         7.8.2       The if-then-else Structure.         7.8.3       The iterative Structure.         7.8.3       The iterative Structure.         7.9       THE TRUTH ABOUT SOFTWARE         7.9.1       Software Quality         7.10       WRITING GOOD PROGRAMS.         7.11       CHAPTER SUMMARY.                                                                                                                         | 169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>171 -<br>173 -<br>175 -<br>176 -<br>177 -<br>178 -<br>178 -<br>179 -<br>180 -<br>180 -<br>183 -<br>183 -<br>183 -                   |

| 7 | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages         7.4       Assembly LANGUAGES: THE GOODNESS OF "LOW-LEVEL"         7.5       PROBLEM SOLVING WITH PROGRAMMING         7.6       STRUCTURED PROGRAMMING         7.7       MOTIVATIONAL DISCUSSION OF FLOWCHARTING         7.7.1       The Basics of Flowcharting         7.7.1       The Basics of Flowcharting         7.8.3       The iterative Structure         7.8.2       The if-then-else Structure         7.8.3       The iterative Structure         7.8.3       The iterative Structure         7.9       THE TRUTH ABOUT SOFTWARE         7.9.1       Software Quality         7.10       WRITING GOOD PROGRAMS         7.11       CHAPTER SUMMARY         7.12       CHAPTER EXERCISES                                                                                              | 169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>171 -<br>173 -<br>175 -<br>176 -<br>177 -<br>178 -<br>179 -<br>179 -<br>179 -<br>180 -<br>180 -<br>183 -<br>184 -                   |

|   | ASSEMBLY LANGUAGE INTRODUCTION         7.1       INTRODUCTION         7.2       BITS TO MNEMONICS AND BACK AGAIN         7.3       PROGRAMMING LANGUAGE LEVELS         7.3.1       Machine Code         7.3.2       Assembly Language         7.3.3       Higher Level Languages         7.4       Assembly Languages         7.4       Assembly Languages: The Goodness of "Low-Level"         7.5       PROBLEM SOLVING WITH PROGRAMMING         7.6       STRUCTURED PROGRAMMING         7.7       MOTIVATIONAL DISCUSSION OF FLOWCHARTING         7.7.1       The Basics of Flowcharting         7.7.1       The Basics of Flowcharting         7.8.3       The iterative Structure         7.8.2       The if-then-else Structure         7.8.3       The iterative Structure         7.8.3       The iterative Structure         7.9.1       Software Quality         7.10       WRITING GOOD PROGRAMS         7.11       CHAPTER SUMMARY         7.12       CHAPTER EXERCISES                                                                                                    | 169 -<br>169 -<br>170 -<br>170 -<br>171 -<br>171 -<br>171 -<br>171 -<br>173 -<br>175 -<br>176 -<br>177 -<br>178 -<br>179 -<br>179 -<br>179 -<br>180 -<br>180 -<br>183 -<br>184 -                   |

| 5                                                                                                            | 3.2                                                                                                                  | INSTRUCTION                                                                                                                                                                                                                                                                                            | SET ARCHITECTURE DESIGN ISSUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - 187 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |